Global high-mix volume high-speed PCBA manufacturer

9:00 -18:00, Mon. - Fri. (GMT+8)

9:00 -12:00, Sat. (GMT+8)

(Except Chinese public holidays)

Global high-mix volume high-speed PCBA manufacturer

9:00 -18:00, Mon. - Fri. (GMT+8)

9:00 -12:00, Sat. (GMT+8)

(Except Chinese public holidays)

HomePage > Blog > Knowledge Base > FPGA vs. CPLD: A Comprehensive Guide to Their Difference

The choice of the right programmable devices determines the outcome of one's project in modern society. There are many programmable logic devices in the electronics field, but this paper will compare Field-Programmable Gate Arrays (FPGAs) and Complex Programmable Logic Devices (CPLDs) in the PCBasic platform. Both types of Programmable Logic Devices (PLDs) help engineers design digital circuits. FPGAs and CPLDs provide efficient and fast prototyping. However, many of the fundamental differences make them more suited to specific needs. In the comparison of FPGAs and CPLDs, examples explain the benefits and drawbacks of this technology. According to a recent market analysis, the global demand for FPGAs is expected to be $9.5 billion by the year 2027, with a compound annual growth rate (CAGR) of 8.6% from 2022 to 2027 (CLOUDERA DOCUMENTATION, 2024).

According to the PCBasic team, our research shows that, in the automobile industry, one of the critical factors is CPLD vs FPGA. Based on the ADAS and electric vehicle control system, there is an annual 25% increase in proper programmable devices.

While FPGAs are used more for high-complexity applications, CPLDs are generally more suited to less complex, cost-sensitive designs. The article will explore the natural market segmentation that arises from the unique strengths of each technology.

The digital design market moved upscale with the introduction of the Field-Programmable Gate Array (FPGA). Like all other PLDs, it is a semiconductor device that has a matrix of configurable logic blocks linked by programmable interconnection.

Imagine an FPGA as a blank digital canvas capable of realizing any digital circuit. This makes them so unique and set apart from other fixed-function chips. Today's FPGAs even have built-in memory blocks and DSP units; they support all major IO standards.

FPGAs can execute multiple operations in parallel and perform millions of operations simultaneously, making them ideal for compute-intensive tasks.

The FPGAs are mainly based on the LUTs, flip-flops, and interconnect matrices. All these components are combined to design complex digital functions. The LUTs work for the logic operations for small-to-table programs and the flip-flops store solutions between steps.

Compared to CPLDs, FPGAs can accommodate large, complex designs requiring significant memory and high-speed processing. Their architecture lends itself easily to advanced features such as clock management, dedicated arithmetic blocks, and on-chip memory, making the FPGA well-suited for all applications, from telecommunications to AI acceleration.

Complex Programmable Logic Devices — CPLDs are relatively simple yet very potent means of programming logic. They are also compact, and it is fast to implement digital circuits based on deterministic timing and instant capabilities.

The Basic Elements of CPLDs Are:

● Logic Implementation by numerous Macro sales.

● The Nonvolatile memory for configuration storage.

● Predictable and simple routing structure

● I/O blocks for external connection

● Programmable interconnect Array.

CPLDs are good for control applications such as state machines and I/O port control because of their deterministic timing and stable performance due to their architectural design, hence becoming perfect for such control applications and blue logic.

CPLD excels in applications requiring fast response times and basic logic operations. Its architecture provides deterministic timing and predictable performance, making it valuable.

CPLDs have nonvolatile memory, meaning they retain their programmed configurations even when power is not available. Most FPGAs, on the other hand, require external memory to operate properly. CPLDs simplify system design and reduce its complexity, hence reducing costs.

CPLDs prove very useful in situations where simplicity and reliability are the prime considerations. Their architecture, being simple, makes them ideal for bus interfacing, simple state machines, and control logic implementation. The predictable tuning features of CPLDs make them valuable in designs requiring precise timing control. CPLDs are most beneficial because they are instant-on, allowing them to operate instantly upon power-up.

The original architectural foundations of PLDs help you learn the key differences between CPLDs and FPGAs. You will discover different ways to implement digital logic by looking inside their internal structures.

These devices get their shape from these architectural elements.

● Logic blocks and their organization

● Memory implementation

● Interconnect Structure and Routing

● I/O capabilities

● Configuration architecture

Follow the three following aspects:

1. Internal structure and components

2. Memory and logic distribution

3. Configuration methods

The internal structures of Programmable Logic devices reveal novel architectural solutions that define their functionalities. Our examination of the FPGA RC texture exposes a complex canvas of components:

● Logical elements with look-up tables

● Flip-flops for sequential logic

● Dedicated DSP blocks for arithmetic operation

● Block RAM modules

● Programmable interconnect matrix

The CPLD architecture is more centralized. Components are arranged in a hub-and-spoke pattern with a central switch matrix connecting to multiple logic blocks. Each of the product terms from the logic block feeds into Macrocells to create an efficient path for signal processing.

The memory and logic distribution patterns are fundamentally different in design implementation between Programmable logic platforms. FPGAs have a highly distributed memory architecture, which provides designers with great flexibility in resource allocation.

CPLDs centralize the way memory is distributed. The DEAR architecture affords deterministic timing at the cost of limited capacity of memory against FPGAs. CPLD logic distribution for the hub-and-spoke pattern that connected resources through a central switch matrix.

FPGAs utilize volatile configuration memory. Your design must be reloaded every time the device powers up. Exit from an external memory source. The process involves:

● SRAM-based configuration storage

● External flash memory needed

● Various programming interfaces( JTAG, SPI, parallel)

● wood time setup loading

● Flexibly reprogrammable options

CPLDs implement configuration in a much simpler manner. On-board nonvolatile memory precludes the requirement for external configuration storage. The same architecture is used twice to provide instant functionality, particularly in system initialization tasks.

About PCBasic

About PCBasic

Time is money in your projects – and PCBasic gets it. PCBasic is a PCB assembly company that delivers fast, flawless results every time. Our comprehensive PCB assembly services include expert engineering support at every step, ensuring top quality in every board. As a leading PCB assembly manufacturer, we provide a one-stop solution that streamlines your supply chain. Partner with our advanced PCB prototype factory for quick turnarounds and superior results you can trust.

After looking at the architectural foundations, let's examine the practical consequences of selecting between CPLDs and FPGAs. Our experience using both Technologies reveals simple trade-offs that define their applicability to different applications.

Through internal layout, the architectural distinctions between FPGAs and CPLDs can be visually compared to show their different approaches. The reason FPGAs perform well in complex memory-intensive applications is illustrated by these architectural renderings. The quickest method for handling simple control tasks that call for quick reaction times is CPLD.

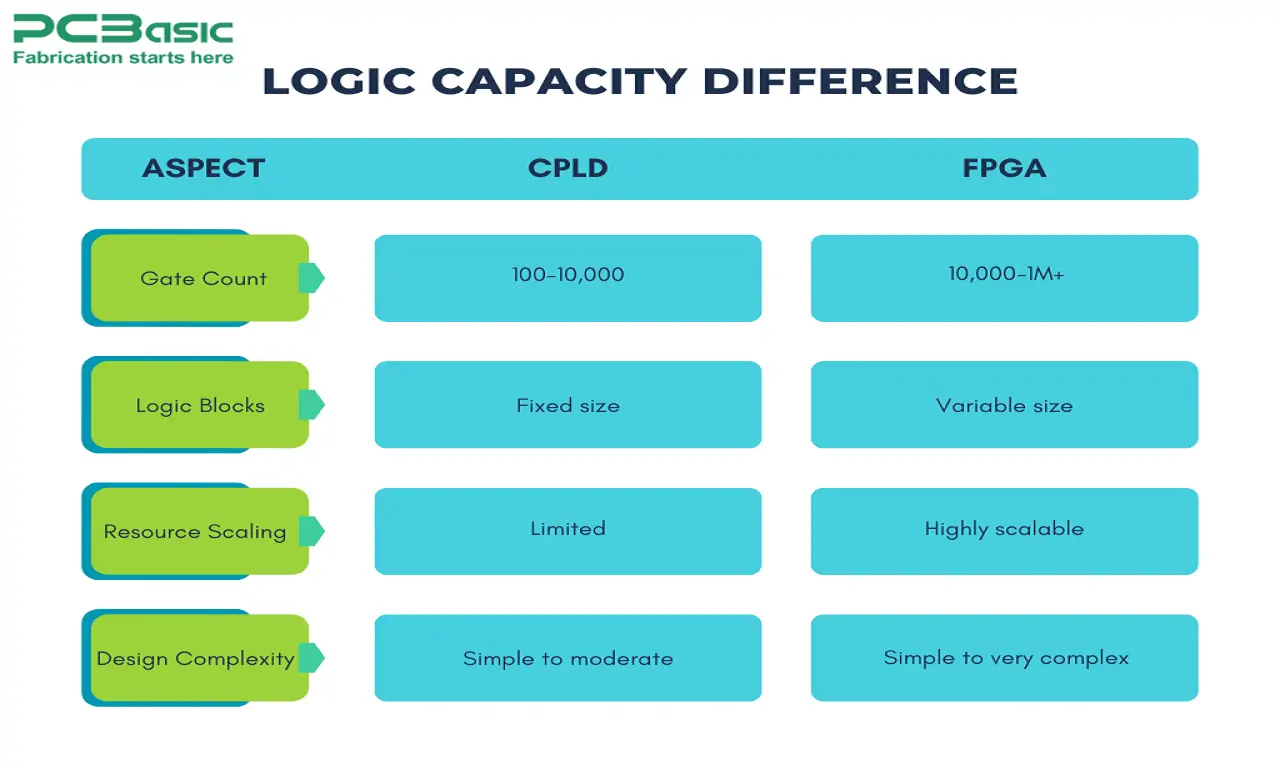

Programmable devices are compared using logic to illustrate that FPGAs and CPLDs are at various levels of complexity. Our practical experience with these devices demonstrates that FPGAs provide tenfold more logic resources than CPLDs.

A summary of common logic resources is provided below:

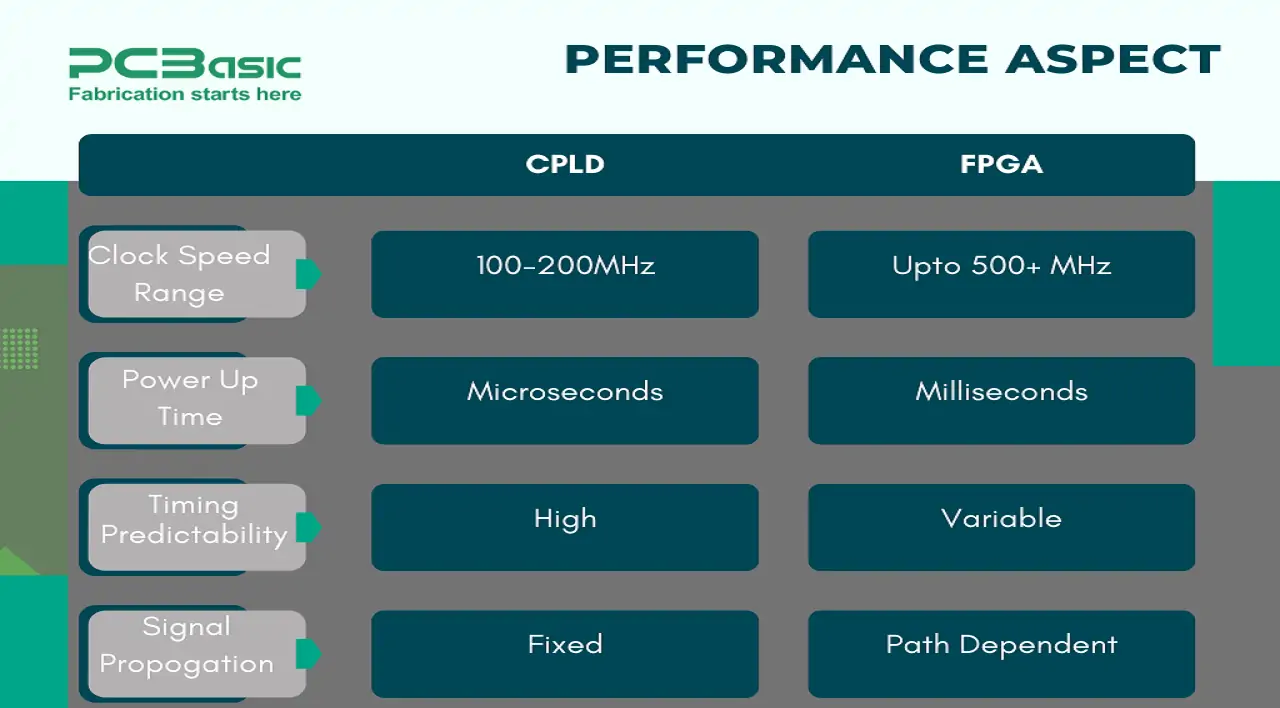

Performance characteristics are the foundations of choosing the right Programmable Logic device for specific applications. Our most extensive longitudinal study shows precise performance profiles for both Technologies.

The comparative metrics we measured show:

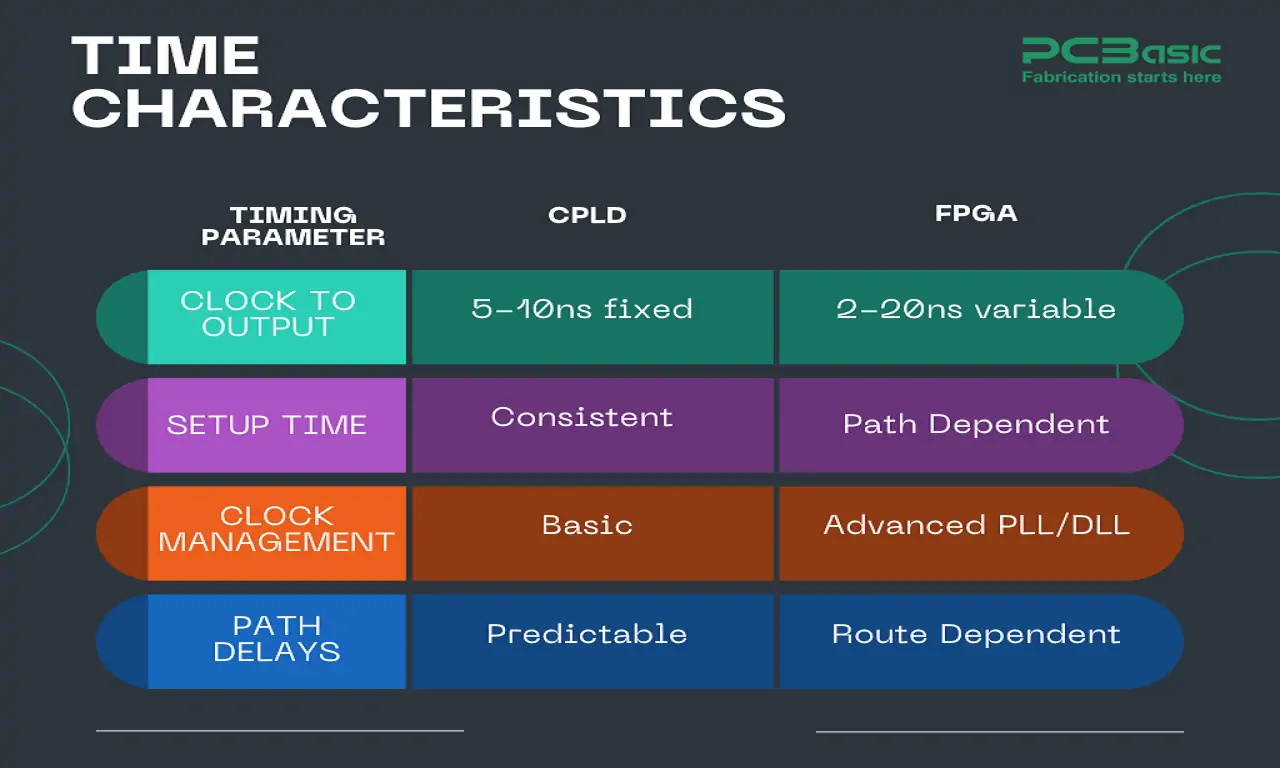

Our left tests of timing characteristics indicate that CPLDs and FPGAs behave differently in signal propagation and clock management.

The characteristics of timing play a crucial role in our interface circuit selection process, which requires strict timing control. In most cases, this can be better achieved using Complex Programmable Logic Devices (CPLDs) because of their predictable nature, especially in those applications that involve higher levels of clock domain management. More sophisticated clock capabilities provided by Field Programmable Gate Arrays (FPGAs) also come in handy for such applications.

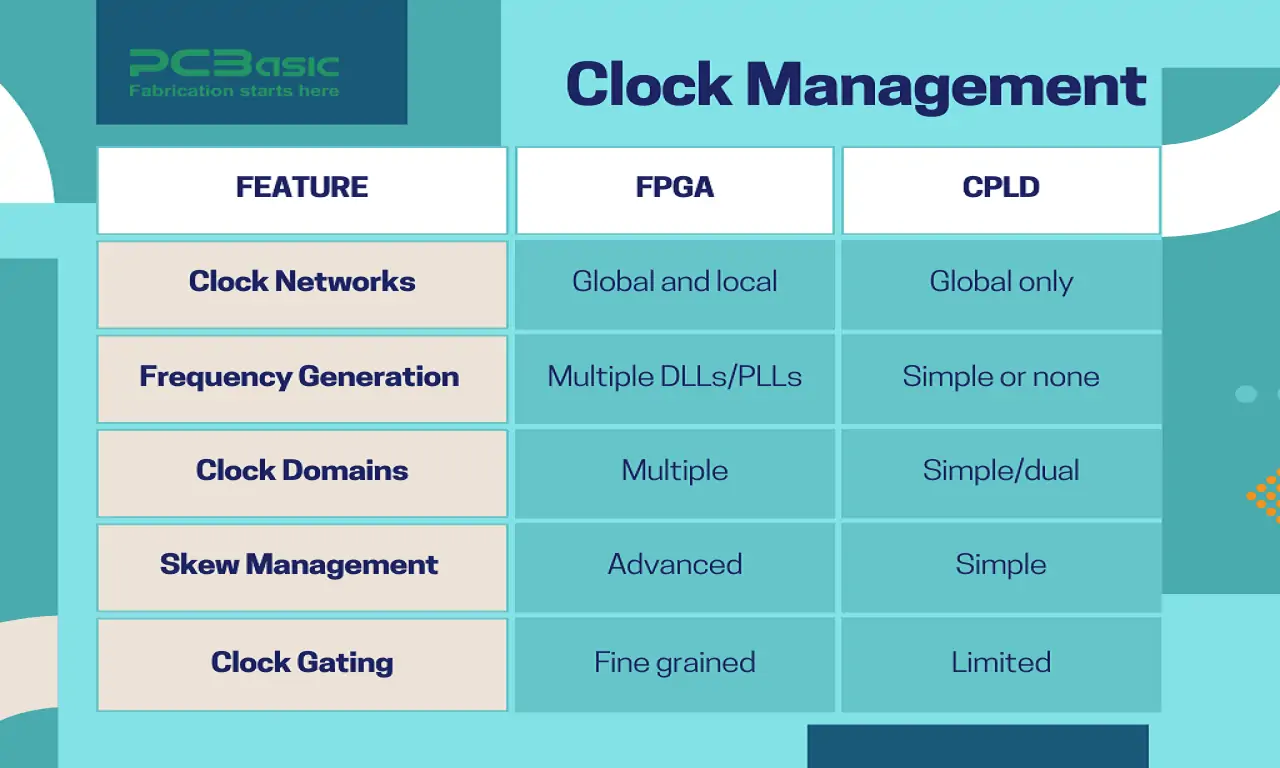

Programmable logic platforms also differ significantly with regards to clock management. Research and practical experience with Field-Programmable Gate Arrays (FPGAs) has demonstrated high-end features related to clock handling, which are well beyond the features of Complex Programmable Logic Devices (CPLDs).

Our study of clock management has revealed the key differences between platforms, pointing out superior functionality inherent in FPGA technology.

While FPGAs need particular attention to the problems of synchronization and metastability when operating in many clock domains, CPLDs have comparatively straightforward clock distribution topologies that prioritize predictable timing behavior above flexibility.

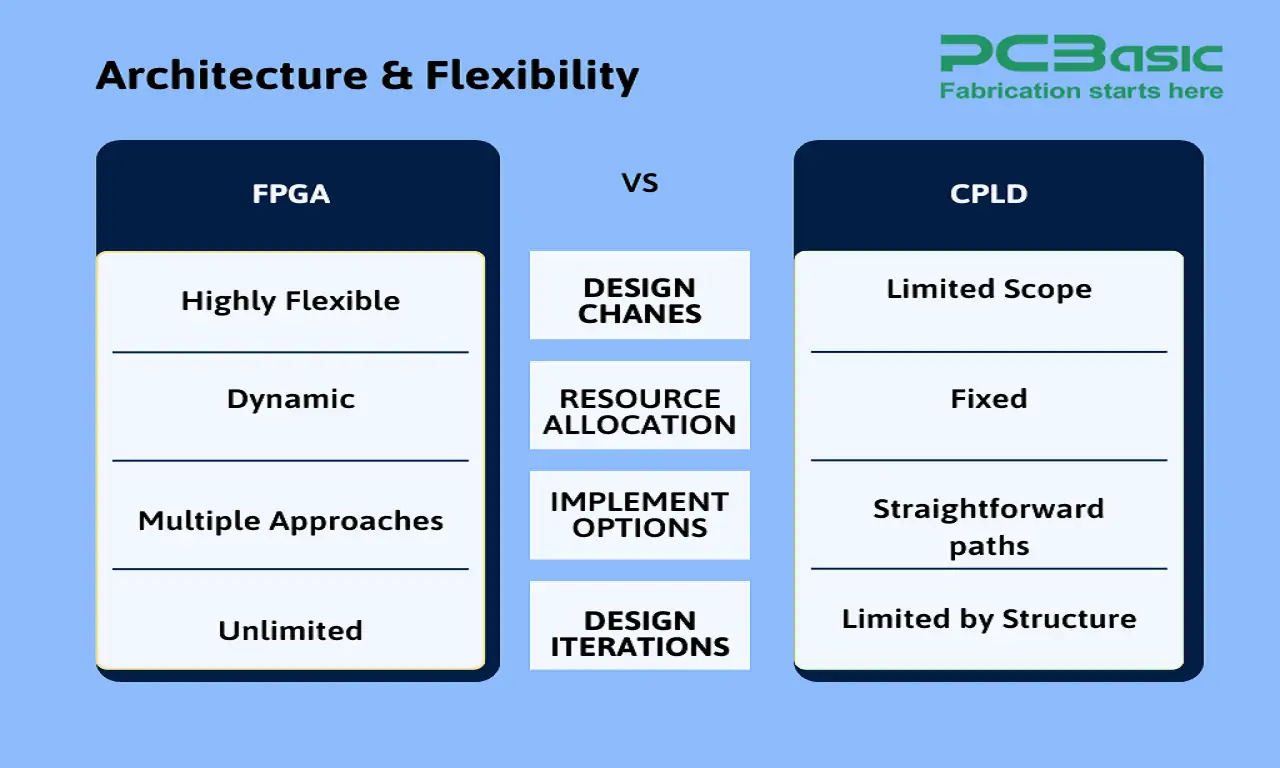

Architectural flexibility of Programmable Logic devices refers to how they accommodate various design requirements. Field-Programmable Gate Arrays (FPGAs) give designers a great deal of autonomy due to their configurable architecture. On the other hand, Complex Programmable Logic Devices (CPLDs) provide targeted flexibility, which is supported by their deterministic design (REVOLVER, 2024).

Here's how architectural flexibility stacks up between devices:

Flexibility variations have a great impact on our development strategies. FPGAs have investigated several implementation methodologies, such as CPLDs, to increase the efficiency of streamlined solutions. This makes CPLD a viable tool for implementing the desired functionalities of the table.

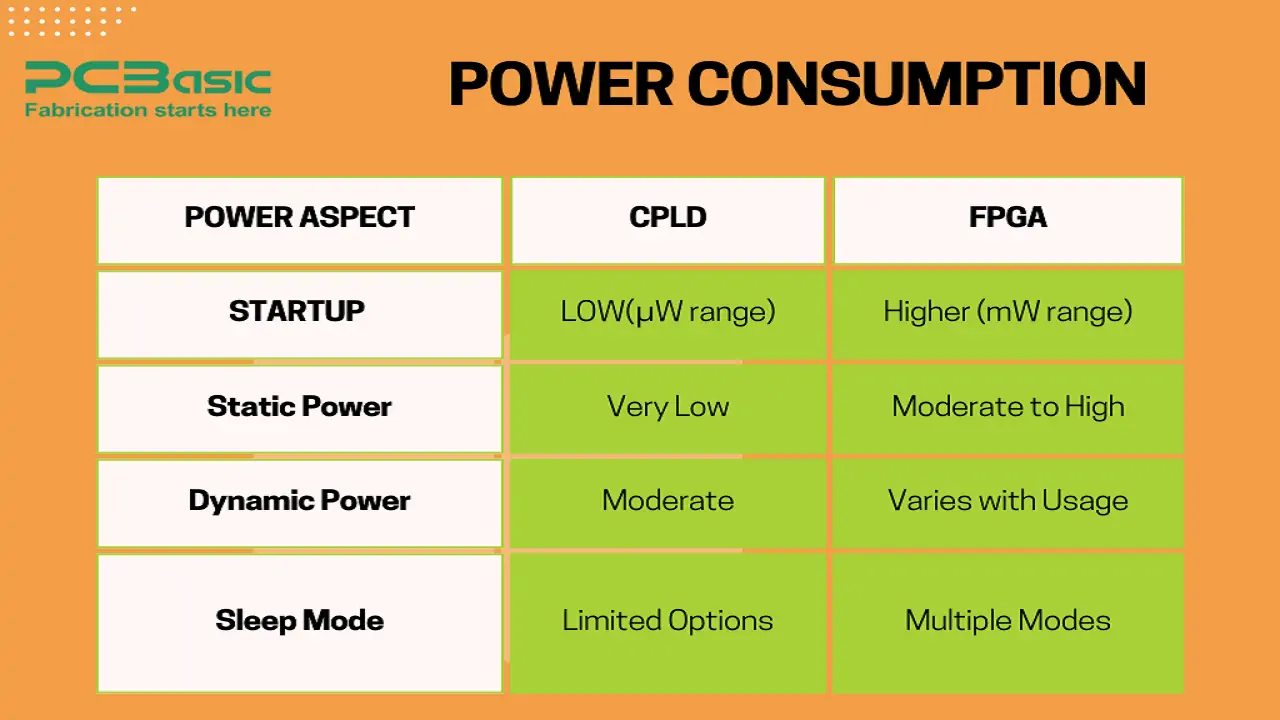

Power efficiency is important in the use of devices for electronic systems. According to our testing and implementation experience, there are noticeable differences in power consumption patterns between cplds and FPGAs, which also impacts system design significantly.

Tests prove that CPLD provides less power immediately than FPGAs, which are ideal for battery-driven systems. Here is what our tests revealed:

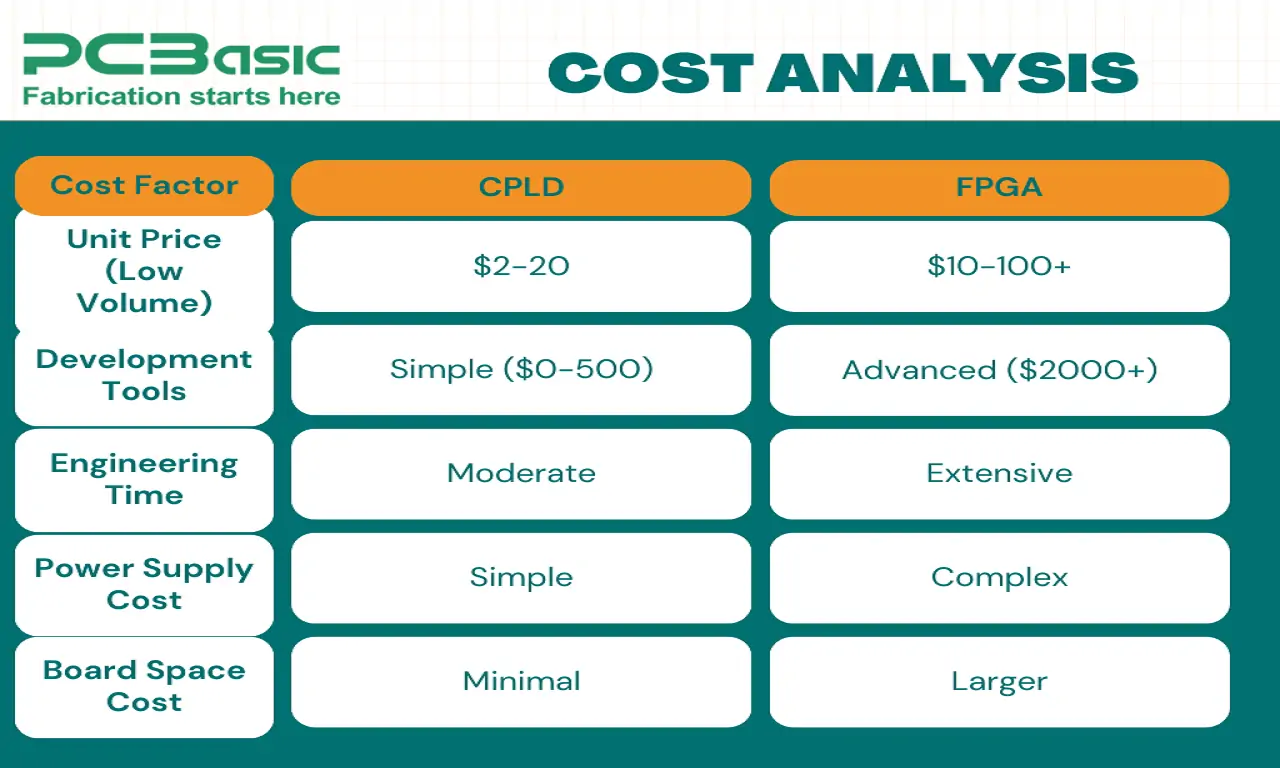

The project budget evaluation shows that the cost exceeds the original device price. Our team knows total investments include development tools, engineering time, and long-term maintenance costs.

there are some factors that we need to look at

● Original hardware investment

● Development tool license

● Engineering research resource requirements

● Production volume pricing

● Maintenance and updates

Here is whatever Cost Analysis reveals:

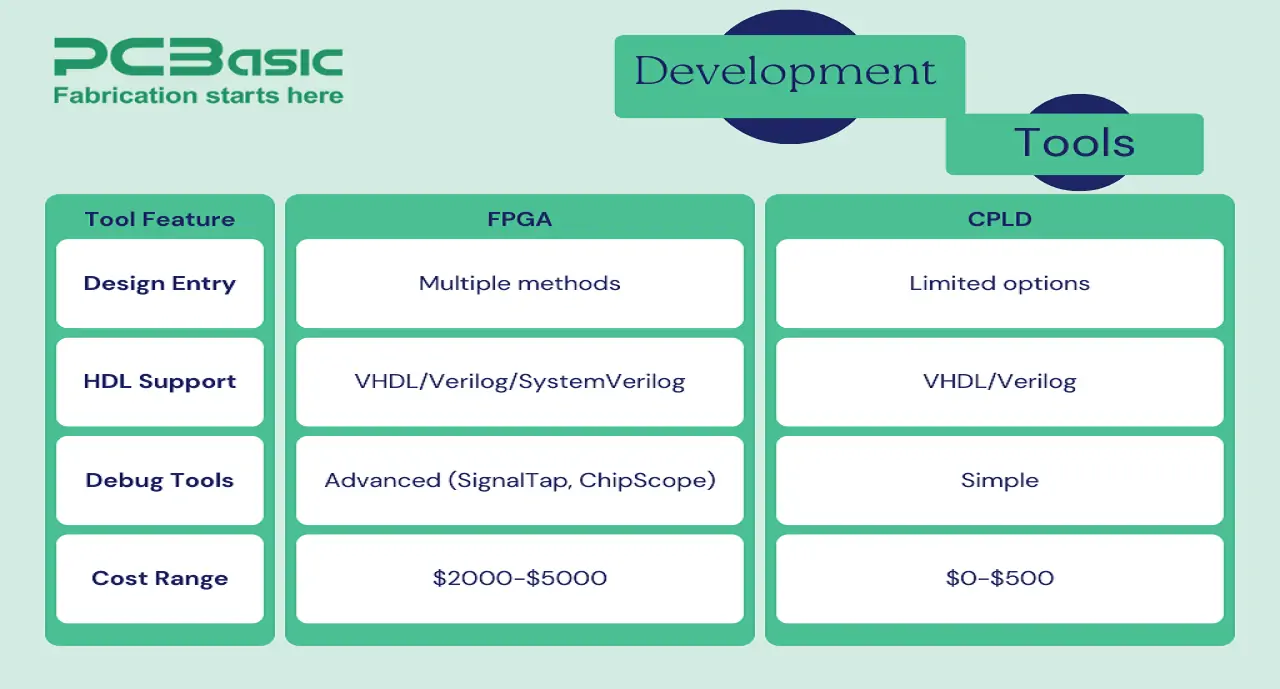

Development environment services are a vital part of our design process. FPGA and CPLD to change have notable differences. FPGA has developed the most sophisticated tools because of its Complex architecture and capabilities.

Our design work depends on several essential development features

● Project version control integration

● Design constraint management

● Power estimation utility

● Timing analysis capabilities

● Integrated synthesis and simulation tools

This complete analysis helps us compare the development environment:

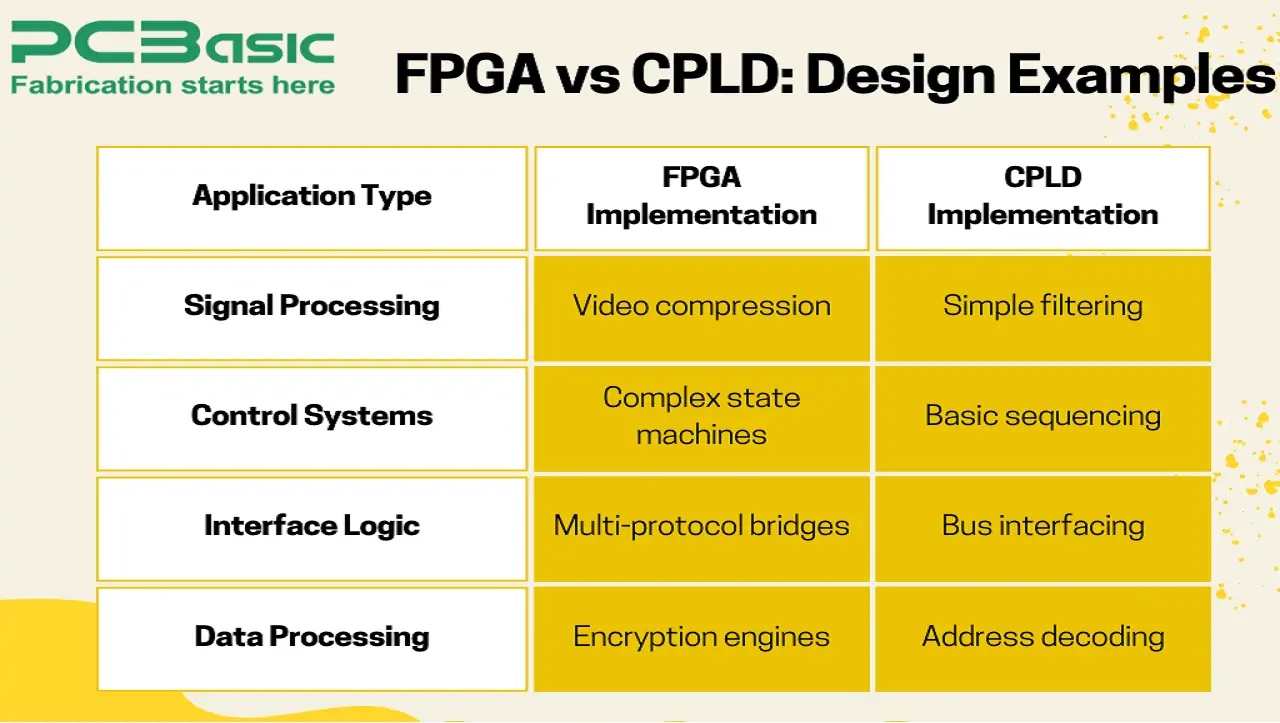

Let's take some examples of ground designs we've used to show the practical differences between these technologies. They help illustrate how differences in architecture guide our application design for different application types.

Some examples of complex router designs that could be done in FPGAs are:

● Multiple parallel processing paths

● Advanced clock management

● Dynamic packet handling

● Live traffic analysis

● Flexible protocol updates

Cpld is very efficient for applications such as LED control systems and motor controllers for more straightforward control applications. Their predictable timing and incidental capabilities are good ways to get scenario results.

Here is how our implementation matches up:

In addition, memory distribution patterns reveal an interesting story regarding Kannada FPGAs-scattering memory resources across the device, much as small story units would be thrown out of a warehouse CPLD with a simple picture of centralized memory blocks that are connected directly to logic arrays.

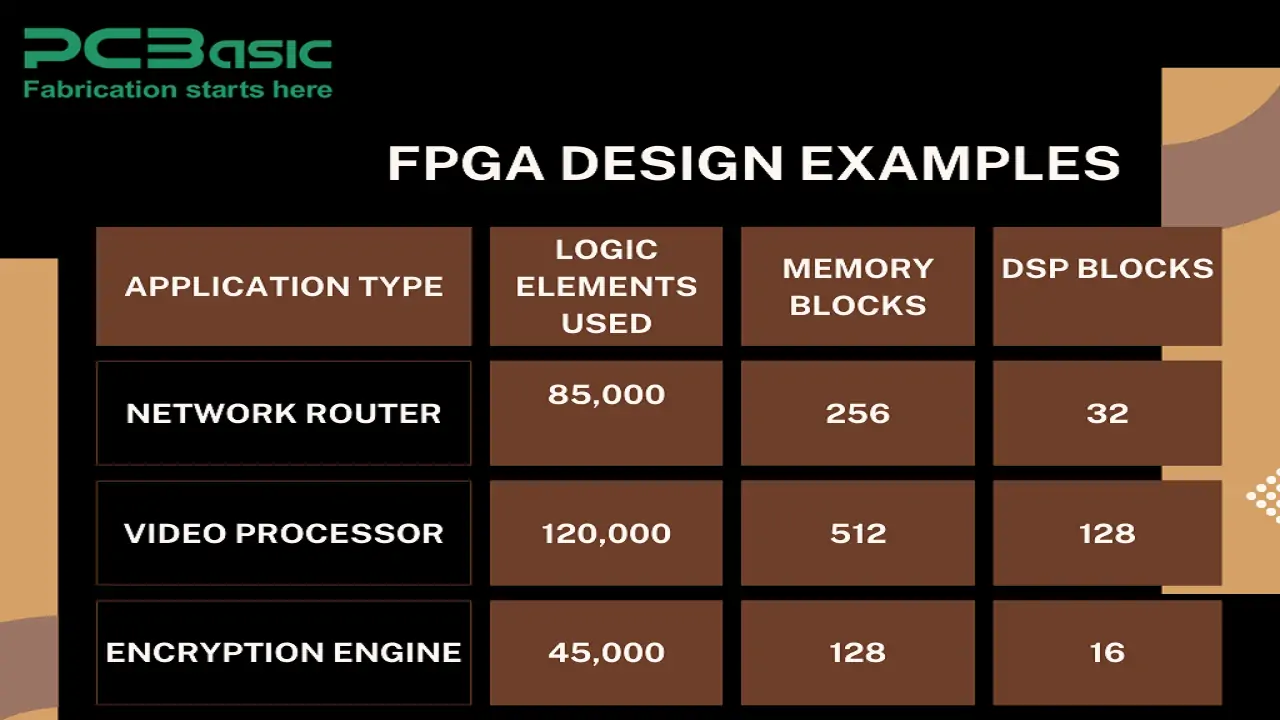

Field-Programmable Gate Arrays (FPGAs) have unique capabilities that enable the creation of many advanced designs. Our work covers a wide range of applications, from high-speed networking to complex signal processing, thus demonstrating the flexibility inherent in FPGA architecture (IBM, 2024).

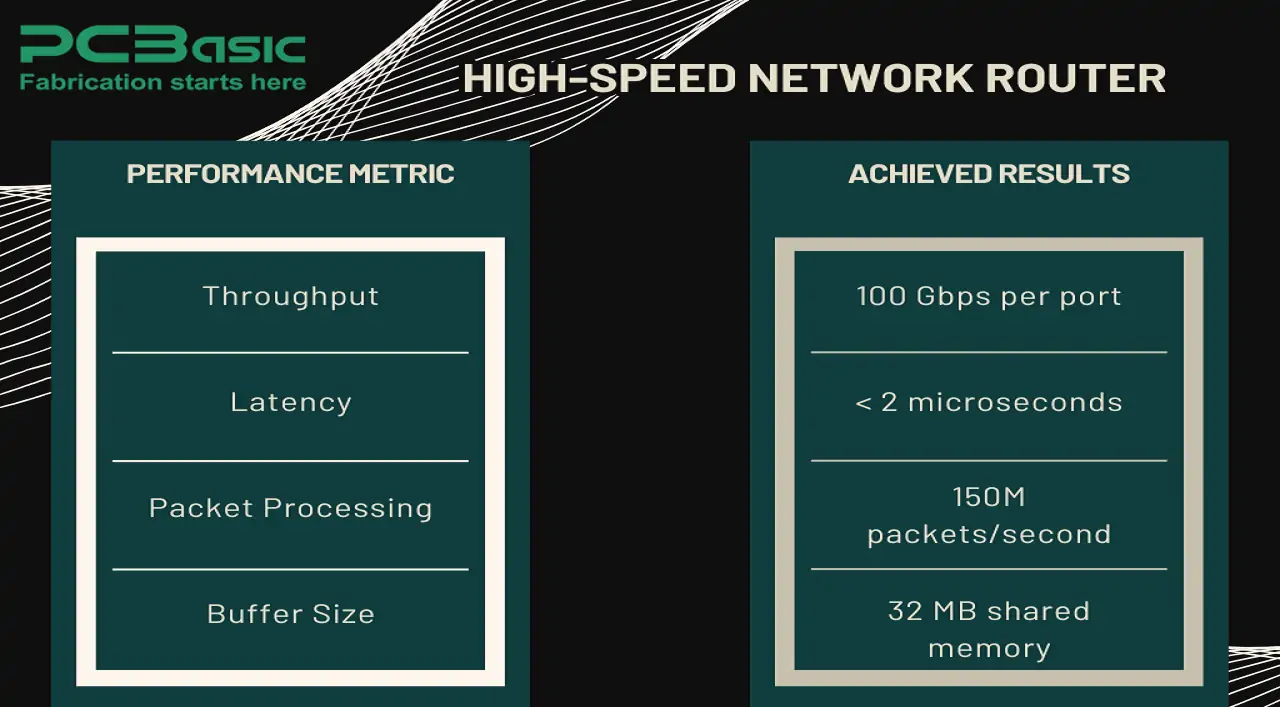

One of our most challenging designs is that of a high-speed network router. In this project, we leveraged the parallel processing power of the FPGA to handle many data streams in parallel, allowing for up to 100 Gbps throughput (IBM, 2024). The design incorporates the following critical functionalities:

● Multi-packet processing engines

● Real-time traffic analysis

● Dynamic routing tables

● Hardware-based encryption

● Quality of Service management

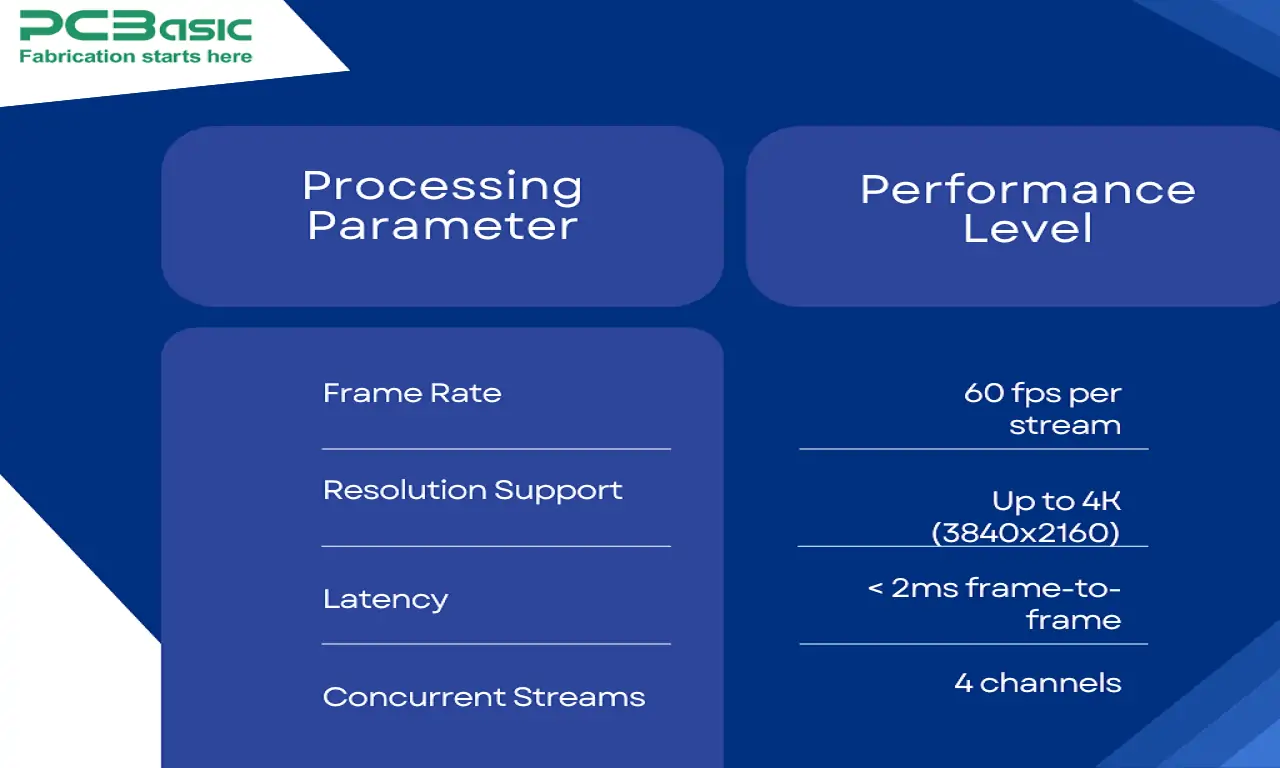

We have developed a real-time video processing system that very effectively demonstrates the superior capabilities of FPGA technology:

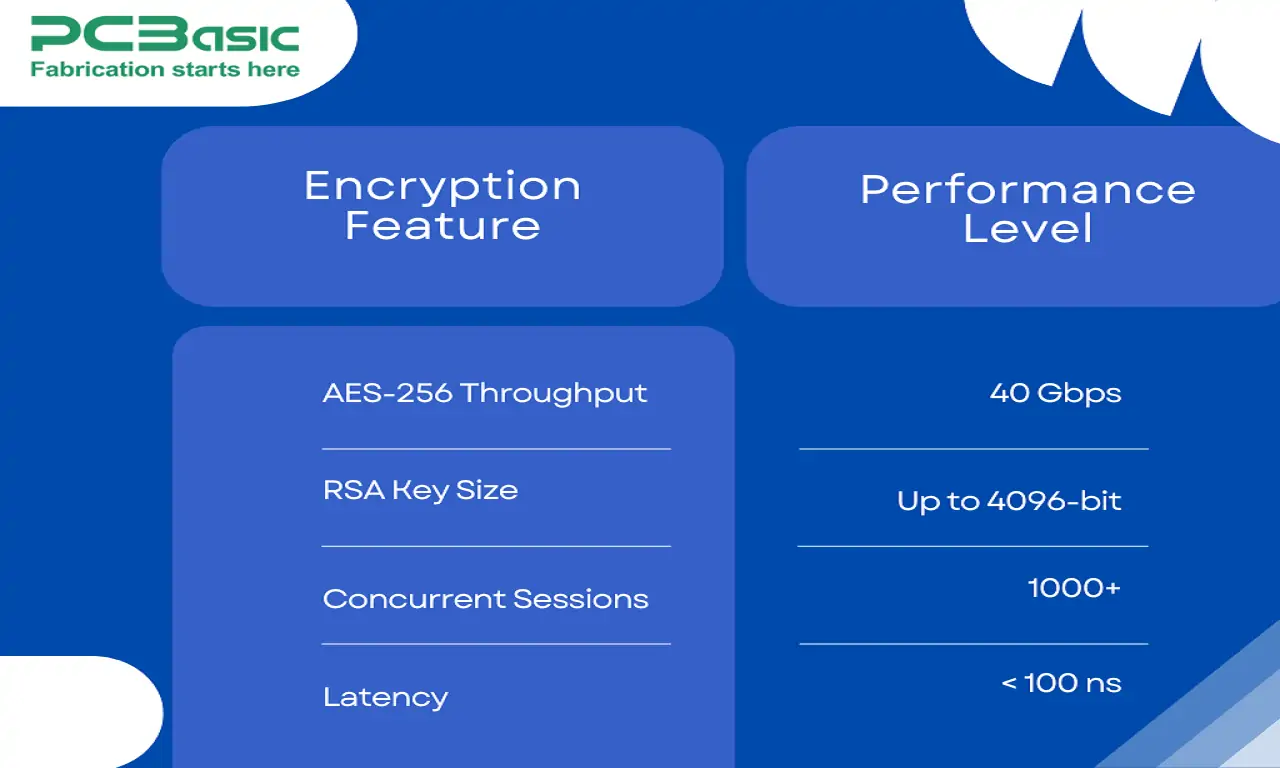

FPGAs are at their best when you require sophisticated encryption acceleration. Our implementation of AES-256 encryption achieves throughput rates substantially higher than software solutions while remaining flexible enough for algorithm updates and security patches.

We built a high-speed network router showing FPGA's advantages over CPLD in complex networking applications. We also had the privilege of working with a Xilinx Ultrascale device; the router operates multiple 100 Gigabit Ethernet ports in parallel.

The design employs FPGA's parallel processing capabilities through the following key components:

● Multi-channel packet processor with dedicated queuing engines

● Hardware-accelerated routing tables for sub-microsecond lookups

● Real-time traffic analysis modules

● Quality of Service (QoS) management system

● Protocol-specific acceleration blocks

Through careful resource allocation, we managed to achieve the following impressive performance metrics:

This shows that FPGAs are much better than CPLDs when complex immediate operations are concerned. The group has also designed a high-end video processing system that can process several video streams in parallel.

The approach can process 4K video streams quickly and gives these performance figures:

It was actually the experience with complex processing tasks that motivated us to design a high-performance encryption accelerator underlining the advanced capabilities of FPGA architecture. The implementation places a premium on secure data processing while providing high throughput rates contemporary cryptographic applications demand.

These performance metrics result from our complete optimization of FPGA resources:

Our extensive experience with CPLDs has provided us with several working, practical implementations that demonstrate their strengths in control applications. These applications explain why CPLDs are still good value for specific design applications even though FPGAs offer much broader capabilities.

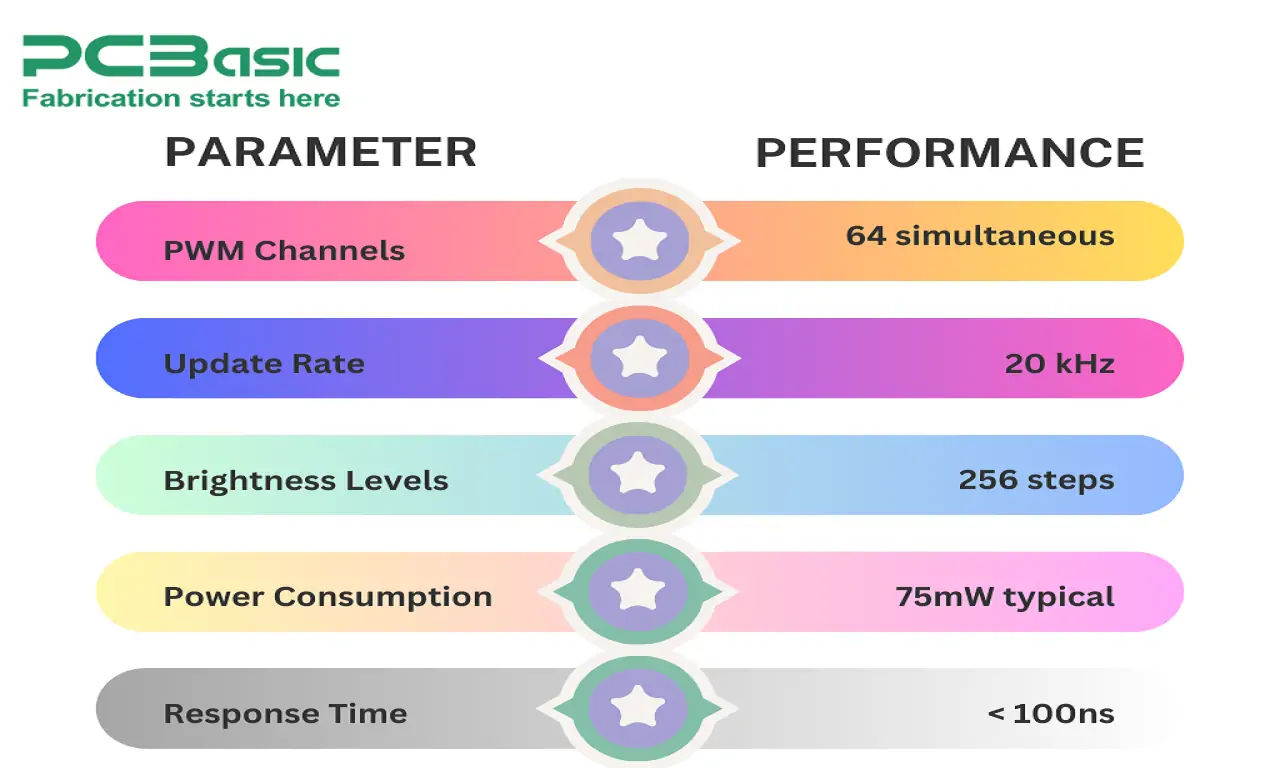

The implementation of our LED controller shows why CPLDs excel in applications that require good timing. The design contains the following features:

● Accurate PWM generation for 64 channels

● Response time measured in sub-microseconds

● Deterministic timing behavior Instant power-up operation

● Low Power Dissipation

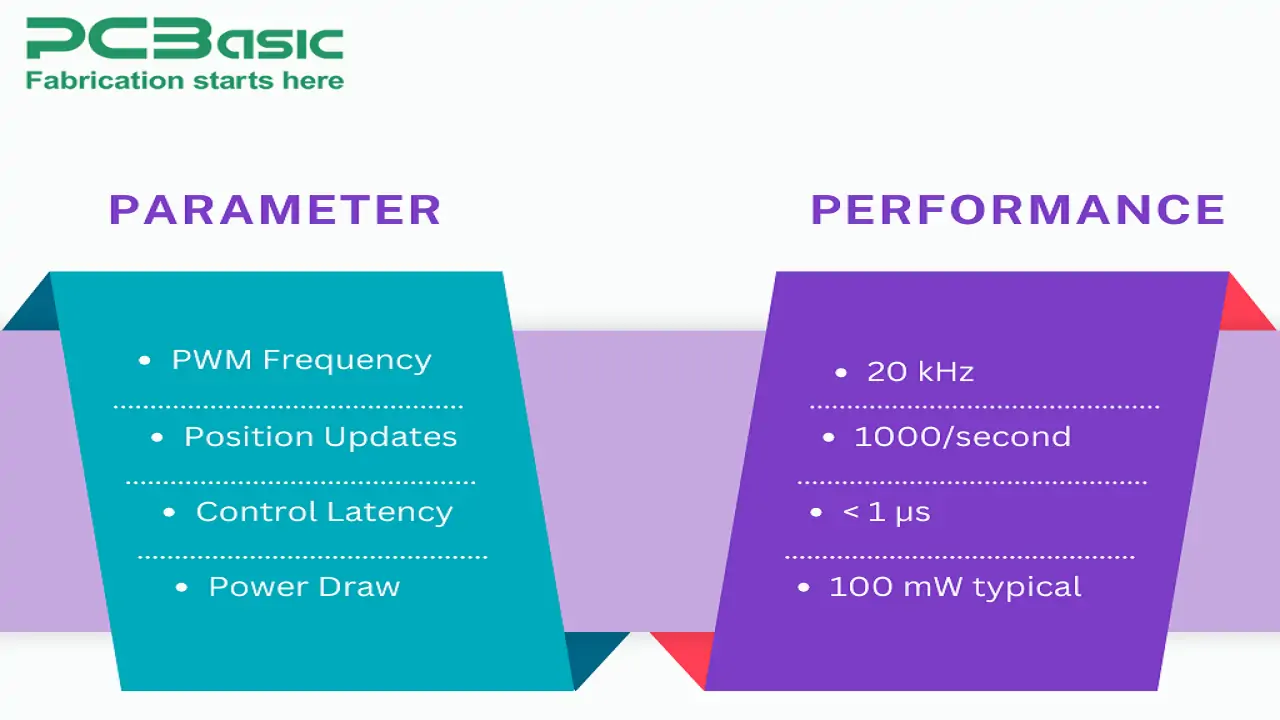

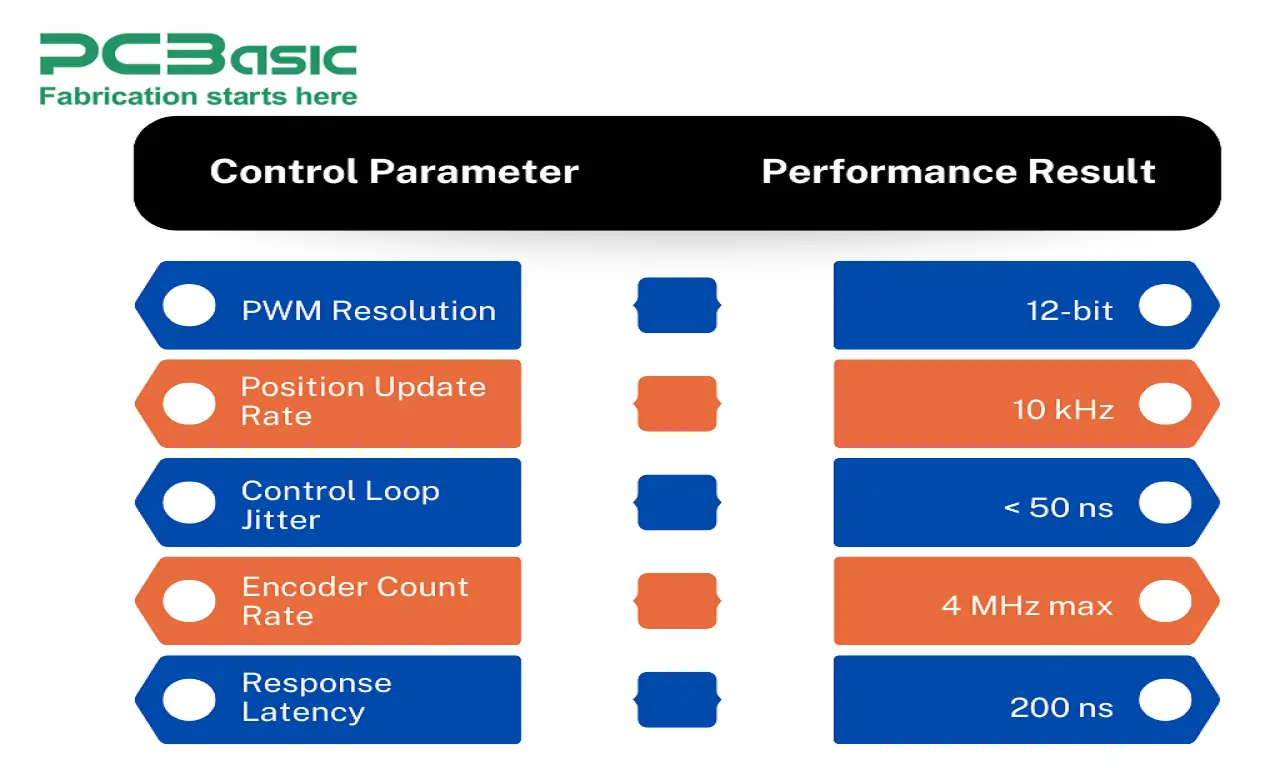

The motor control application exploits the predictable timing of the CPLD for accurate motion control (Lin, Zhuangsheng, 2018). The following details the performance parameters:

Our latest LED controller project has proven why CPLDs are superior for precision timing applications. The implementation manages multiple LED arrays efficiently and is the perfect match between CPLD architecture and real-time control requirements.

Metrics that verify our choice of CPLD over FPGA for this particular application:

Advanced features, including brightness ramping and pattern generation, have been added without compromising the core control timing of the controller. The mid-range CPLD's resources are used by just 65%. This offers tremendous scope for supplemental control functions, which remain deterministically ensured.

This successful implementation reinforces our approach to device selection. We choose the right tool for specific requirements rather than defaulting to the most potent option. CPLDs' straightforward architecture delivers reliable, predictable, and efficient performance in LED control applications.

The motor controller designed for applications with precision motion control clearly points to the advantage of using a CPLD instead of an FPGA. The design, in fact, was done more with a special focus on dealing with stepper and servo motor control, where very accurate timing is demanded and quick responses are critical.

We were able to obtain great implementation metrics based on our decisions about CPLD resources optimizations:

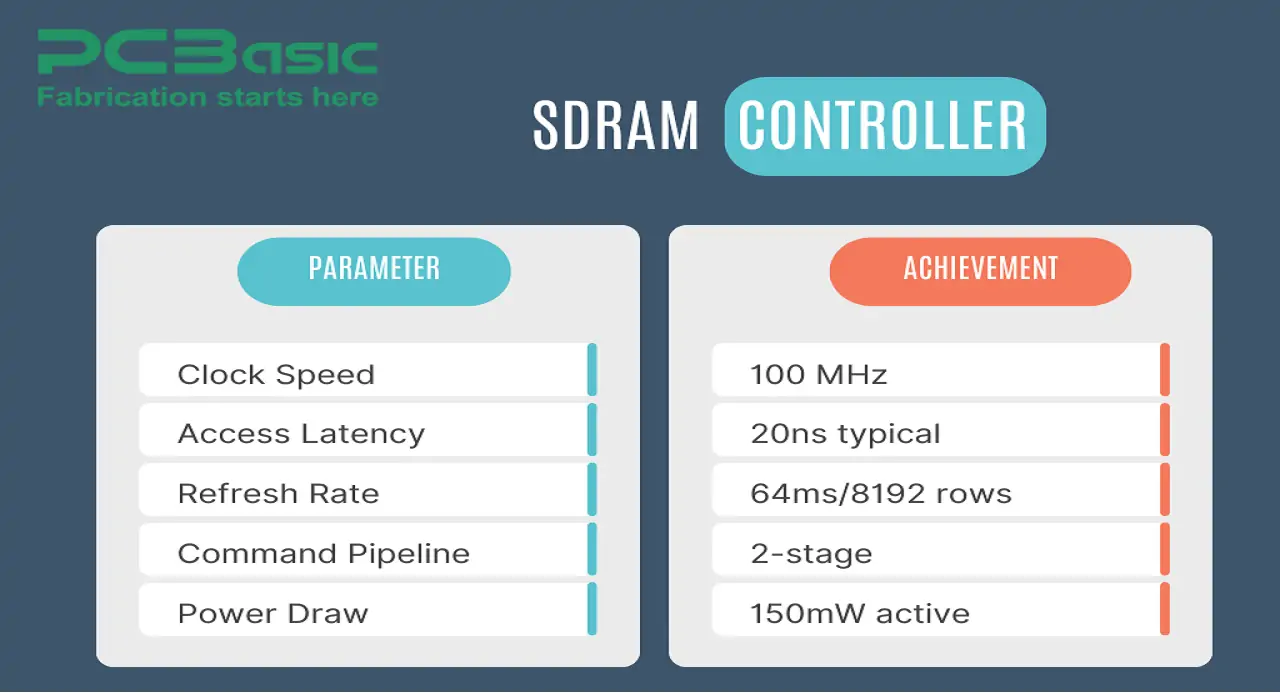

It perfectly balances the CPLD capabilities with the requirements of the memory interface. It is capable of managing high-speed SDRAM modules strictly under stringent timing parameters necessary to guarantee reliable operation of memory.

The figures are valid measures proving that the CPLD can be used appropriately for memory control applications:

The implementation consumes approximately 80% of the resources of a mid-range CPLD and provides reliable performance in memory-intensive applications. The instant-on feature is very beneficial for systems that require memory access to take place immediately after power-up. Otherwise, FPGA-based controllers would consume additional configuration time.

Choices between CPLD and FPGA have very little to do with raw processing power. Simple architectures of CPLDs offer clearer advantages, compared with complex FPGA implementations, where the timing precision and the behavior on startup matter most.

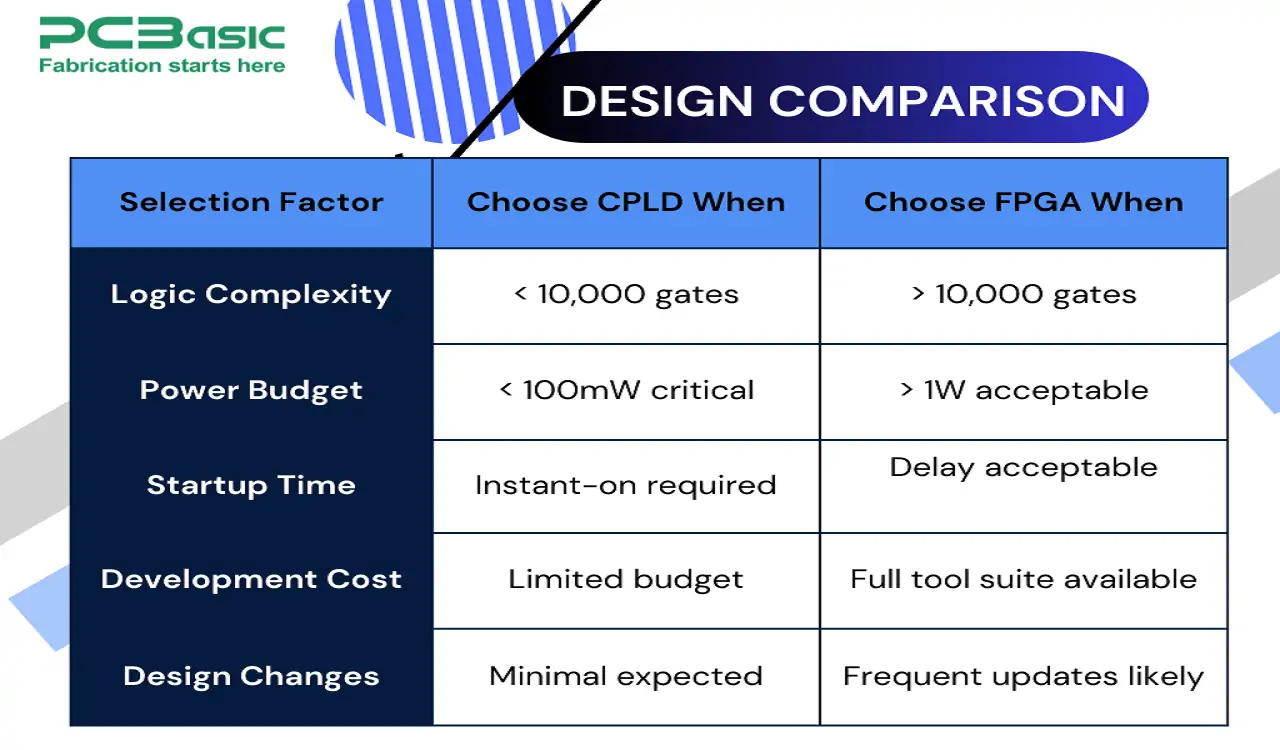

The demands and constraints of your project must be carefully considered before choosing between CPLD and FPGA. Successful device selection requires an understanding of both technical and practical elements.

These crucial elements influence our choice:

● Scale and complexity of the project

● Requirements for power consumption

● Timeline and budget for development

● Performance standards

● Long-term upkeep requirements

We've learned from years of design work what the greatest technologies are.

Let's see how these choices align:

The work of our team on complex digital systems has shown us some specific cases where FPGAs are the best choice. In the process of evaluating the requirements of a project, the core team discovers key indicators of FPGA capabilities:

● Complex data processing requirements

● Multiple interface protocols

● High-speed serial communications

● Advanced timing management needs

● Future scalability requirements

Projects that involve complex signal processing or handling of multiple high-speed interfaces are best done with FPGAs. Live video processing, network packet handling, or even complex encryption requires significant parallel processing that can be found in FPGAs.

For complicated digital systems, we begin our FPGA selection process by thoroughly examining the application requirements. The fundamental elements that make an FPGA superior to a CPLD or microcontroller have been taught to us by project experience over the past few years.

These essential requirements are the focus of our application evaluation:

● Data processing complexity and throughput needs

● Interface protocol flexibility requirements

● Live processing capabilities

● System scalability expectations

● Resource utilization projections

We've built a complete metrics framework to review FPGA suitability in different applications:

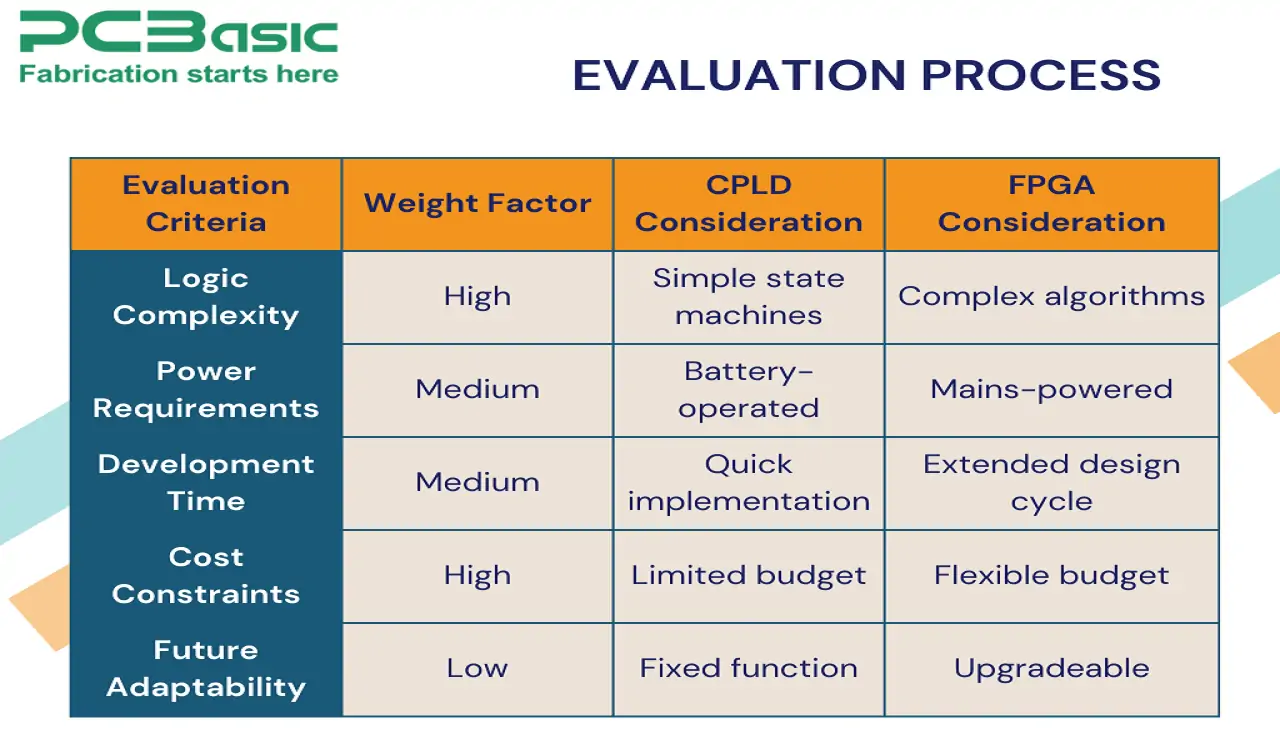

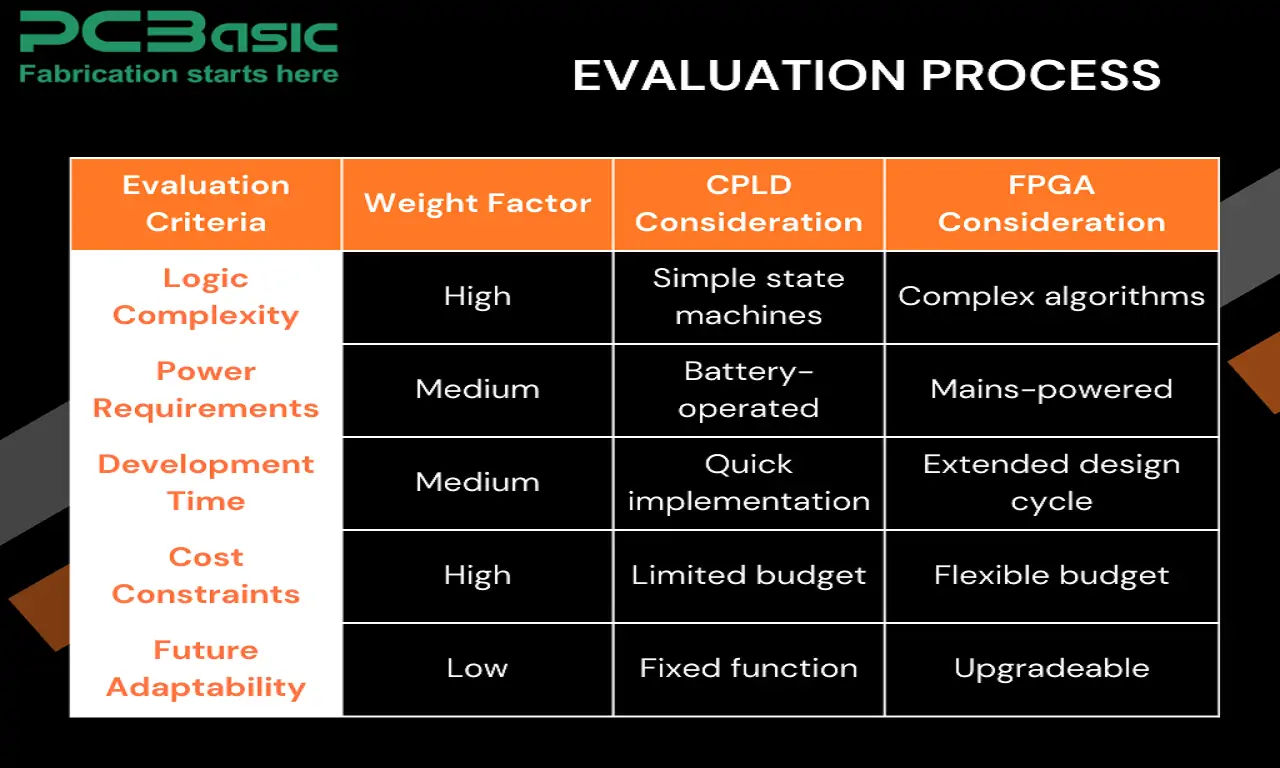

Design teams use our proven evaluation process to make wise decisions about programmable logic devices. We've built this approach over the last several years through hands-on experience with CPLD and FPGA implementations.

The right device selection depends on these key evaluation steps:

● Technical requirement analysis and documentation

● Resource utilization estimation

● Power budget calculation

● Development timeline assessment

● Cost-benefit analysis across project lifecycle

● Tool availability and team expertise evaluation

Our detailed evaluation matrix helps teams make better decisions:

Our digital design experience over the last several years has shown us exactly where CPLDs excel in our projects. We prioritize applications that need reliability and simple functionality rather than complex features.

Projects that use CPLDs include:

● Instant-on capabilities

● Deterministic timing behavior

● Implementation of a simple state machine

● Replacement of glue logic

● Applications that are sensitive to power

● Less expensive options for simple control

Because of our real-world expertise, we have developed a thorough selection matrix.

Examining the application requirements for intricate digital systems is the first step in our FPGA selection process. Project experience over the last several years has taught us the core factors that make an FPGA better suited than a CPLD or microcontroller.

Our application assessment focuses on these key requirements:

● Data processing complexity and throughput needs

● Interface protocol flexibility requirements

● Live processing capabilities

● System scalability expectations

● Resource utilization projections

We've built a complete metrics framework to review FPGA suitability in different applications:

|

Feature |

CPLD |

FPGA |

|

Architecture |

||

|

Logic Capacity |

100-10,000 gates |

10,000-1M+ gates |

|

Memory Structure |

Centralized, nonvolatile |

Distributed, volatile |

|

Routing Architecture |

Hub and spoke, centralized |

Grid matrix, distributed mesh |

|

Performance |

||

|

Clock Speed Range |

100-200 MHz |

Up to 500+ MHz |

|

Power-up Time |

Microseconds |

Milliseconds |

|

Timing Predictability |

High, fixed delays |

Variable, path-dependent |

|

Clock Management |

Simple or none |

Advanced PLL/DLL support |

|

Power |

||

|

Startup Power |

Low (μW range) |

Higher (mW range) |

|

Static Power |

Very Low |

Moderate to High |

|

Dynamic Power |

Moderate |

Varies with usage |

|

Development |

||

|

Tool Cost |

Simple ($0-500) |

Advanced ($2000+) |

|

Design Complexity |

Simple to moderate |

Simple to very complex |

|

HDL Support |

VHDL/Verilog |

VHDL/Verilog/SystemVerilog |

|

Debug Capabilities |

Simple |

Advance (SignalTap, ChipScope) |

|

Applications |

||

|

Ideal Use Cases |

Control systems, glue logic, interface control |

Signal processing, networking, video processing |

|

Design Changes |

Limited scope |

Highly flexible |

|

Implementation Options |

Direct paths |

Multiple approaches |

|

Resource Allocation |

Fixed |

Dynamic |

Design teams use our proven evaluation process to make wise decisions about programmable logic devices. Over the past few years, we have developed this method via practical experience with FPGA and CPLD implementations.

The right device selection depends on these key evaluation steps:

● Technical requirement analysis and documentation

● Resource utilization estimation

● Power budget calculation

● Development timeline assessment

● Cost-benefit analysis across project lifecycle

● Tool availability and team expertise evaluation

Our detailed evaluation matrix helps teams make better decisions:

We draw several crucial conclusions from our investigation of the complexities of programmable logic devices when deciding between CPLDs and FPGAs. The decision-making process include a thorough analysis of both practical constraints and technical specifications.

These crucial elements determine the success of the project:

Application Complexity: While CPLDs are more appropriate for basic control applications, FPGAs are superior at managing data-intensive activities and intricate algorithms. Field-programmable gate arrays, or FPGAs, are very good at processing large amounts of data and putting complicated algorithms into practice. Complex programmable logic devices (CPLDs), on the other hand, are best suited for simpler control applications.

Time Restrictions: CPLDs are an excellent option for system initiation because of their instant-on capabilities and predictable time.

Resource Constraints: FPGAs are usually suited for programs where less than 10,000 gates are needed.

Aspects of Power: The low power consumption profile of CPLD is often beneficial in battery-powered applications.

Development Resources: FPGA projects require more money and experience.

Our experience with both technologies has taught us that success is all about selecting the best solution, not necessarily the most powerful one. CPLDs will remain the reliable workhorse for control-oriented applications; however, FPGAs are gaining unparalleled processing power and versatility.

Both technologies appear to have bright futures ahead. While CPLDs will find their niche in applications that are timing-critical and power-sensitive, FPGAs are likely to branch out into new fields such as artificial intelligence acceleration. When such unique skills are matched with specific needs, successful projects are the result, ensuring peak performance without adding needless complexity.

Assembly Enquiry

Instant Quote

Phone contact

+86-755-27218592

In addition, we've prepared a Help Center. We recommend checking it before reaching out, as your question and its answer may already be clearly explained there.

Wechat Support

In addition, we've prepared a Help Center. We recommend checking it before reaching out, as your question and its answer may already be clearly explained there.

WhatsApp Support

In addition, we've prepared a Help Center. We recommend checking it before reaching out, as your question and its answer may already be clearly explained there.